*C. DOCUMENTATION TECHNIQUE***Annexe A1**

Extraits de la documentation constructeur de l'accéléromètre LIS331DLH.

**Description générale****LIS331DLH**

MEMS digital output motion sensor

ultra low-power high performance 3-axes "nano" accelerometer

**Features**

- Wide supply voltage, 2.16 V to 3.6 V

- Low voltage compatible IOs, 1.8 V

- Ultra low-power mode consumption down to 10  $\mu$ A

- $\pm 2g/\pm 4g/\pm 8g$  dynamically selectable full-scale

- I<sup>2</sup>C/SPI digital output interface

- 16 bit data output

- 2 independent programmable interrupt generators for free-fall and motion detection

- Sleep to wake-up function

- 6D orientation detection

- Embedded self-test

- 10000 g high shock survivability

- ECOPACK® RoHS and "Green" compliant (see Section 8)

**Applications**

- Motion activated functions

- Free-fall detection

- Intelligent power saving for handheld devices

- Pedometer

- Display orientation

- Gaming and virtual reality input devices

- Impact recognition and logging

- Vibration monitoring and compensation

LGA 16 (3x3x1 mm)

**Description**

The LIS331DLH is an ultra low-power high performance three axes linear accelerometer belonging to the "nano" family, with digital I<sup>2</sup>C/SPI serial interface standard output.

The device features ultra low-power operational modes that allow advanced power saving and smart sleep to wake-up functions.

The LIS331DLH has dynamically user selectable full scales of  $\pm 2g/\pm 4g/\pm 8g$  and it is capable of measuring accelerations with output data rates from 0.5 Hz to 1 kHz.

The self-test capability allows the user to check the functioning of the sensor in the final application.

The device may be configured to generate interrupt signal by inertial wake-up/free-fall events as well as by the position of the device itself. Thresholds and timing of interrupt generators are programmable by the end user on the fly.

The LIS331DLH is available in small thin plastic land grid array package (LGA) and it is guaranteed to operate over an extended temperature range from -40 °C to +85 °C.

**Table 1. Device summary**

| Order codes | Temperature range [°C] | Package | Packaging     |

|-------------|------------------------|---------|---------------|

| LIS331DLH   | -40 to +85             | LGA 16  | Tray          |

| LIS331DLHTR | -40 to +85             | LGA 16  | Tape and reel |

## 1 Block diagram and pin description

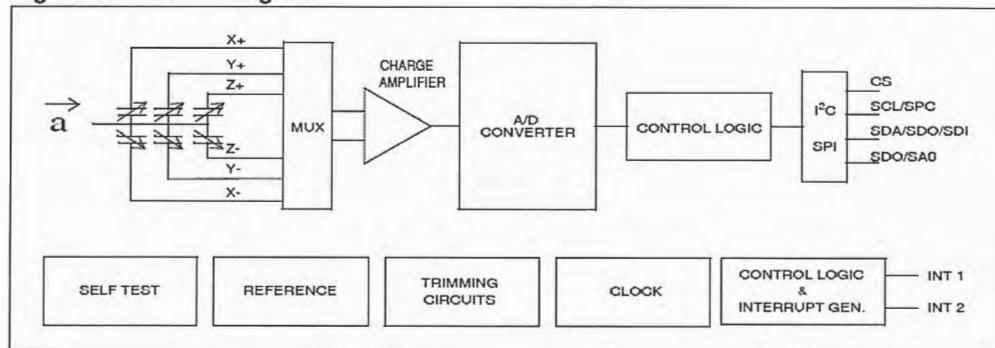

### 1.1 Block diagram

Figure 1. Block diagram

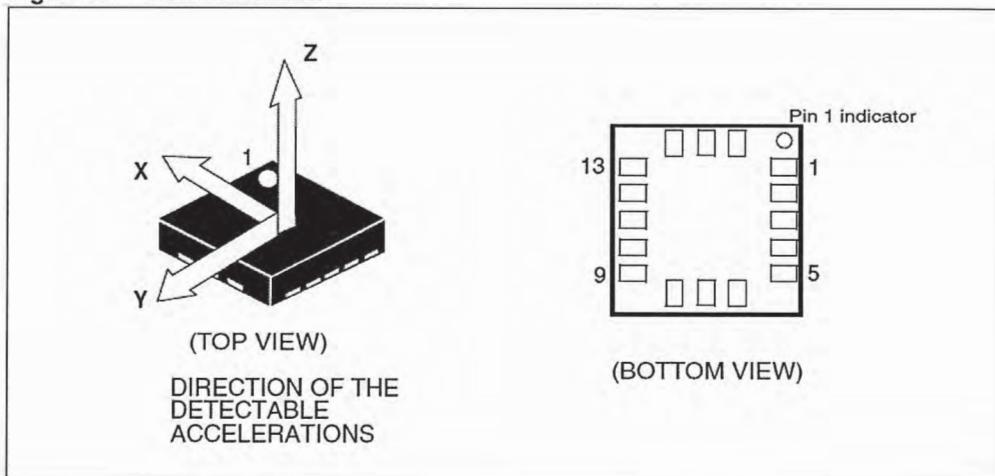

### 1.2 Pin description

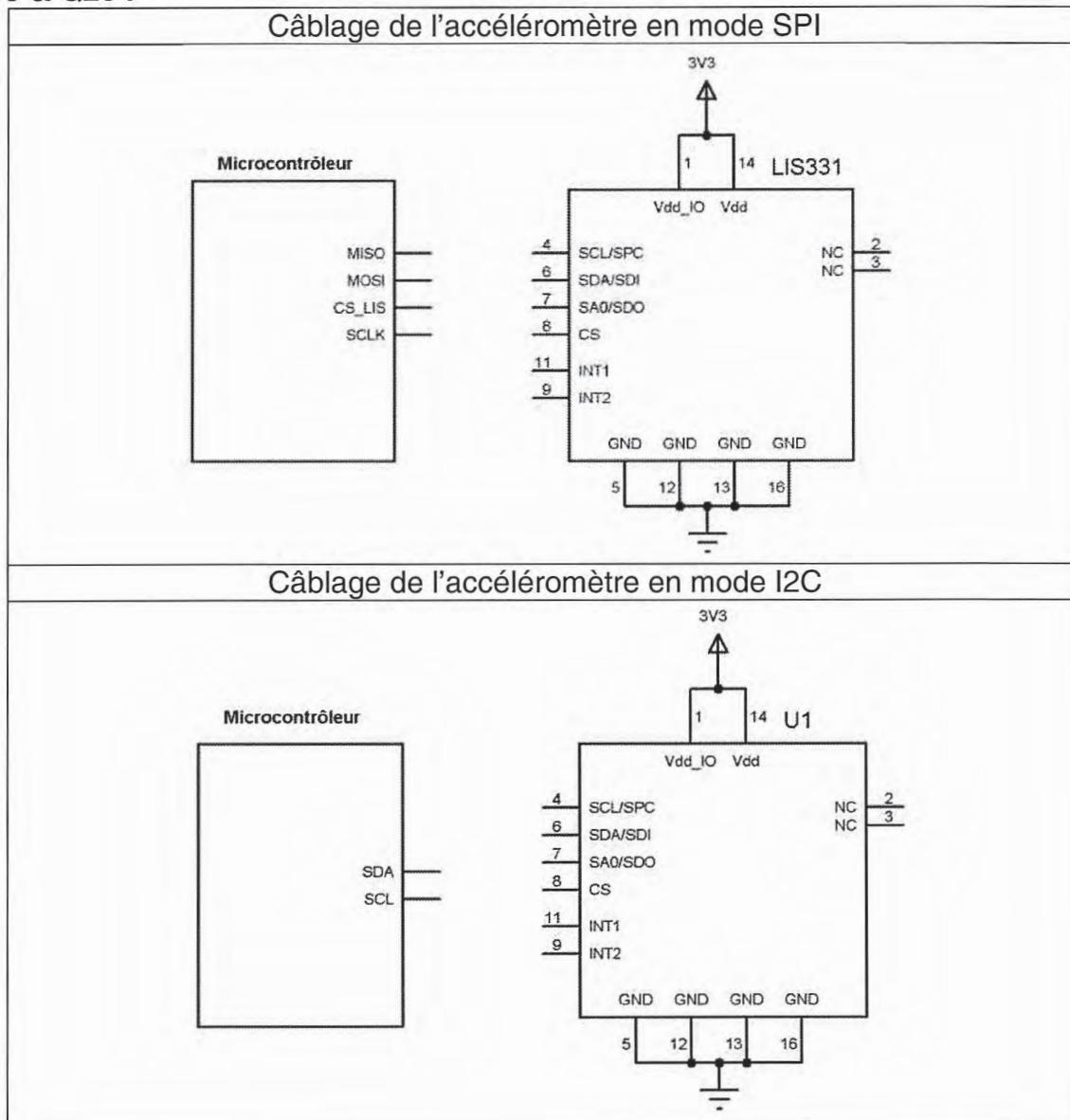

Figure 2. Pin connection

**Plage de mesure et de sensibilité**, en fonction de la valeur stockée dans les bits FS1 et FS0 du registre CTRL\_REG4(23h) :

Table 3. Mechanical characteristics @ Vdd = 2.5 V, T = 25 °C unless otherwise noted <sup>(1)</sup>

| Symbol | Parameter                                                       | Test conditions                           | Min. | Typ. <sup>(2)</sup> | Max. | Unit     |

|--------|-----------------------------------------------------------------|-------------------------------------------|------|---------------------|------|----------|

| FS     | Measurement range <sup>(3)</sup>                                | FS bit set to 00                          |      | ±2.0                |      | <i>g</i> |

|        |                                                                 | FS bit set to 01                          |      | ±4.0                |      |          |

|        |                                                                 | FS bit set to 11                          |      | ±8.0                |      |          |

| So     | Sensitivity                                                     | FS bit set to 00<br>12 bit representation | 0.9  | 1                   | 1.1  | mg/digit |

|        |                                                                 | FS bit set to 01<br>12 bit representation | 1.8  | 2                   | 2.2  |          |

|        |                                                                 | FS bit set to 11<br>12 bit representation | 3.5  | 3.9                 | 4.3  |          |

| TCSo   | Sensitivity change vs temperature                               | FS bit set to 00                          |      | ±0.01               |      | %/°C     |

| TyOff  | Typical zero- <i>g</i> level offset accuracy <sup>(4),(5)</sup> | FS bit set to 00                          |      | ±20                 |      | mg       |

| TCOff  | Zero- <i>g</i> level change vs temperature                      | Max delta from 25 °C                      |      | ±0.1                |      | mg/°C    |

| An     | Acceleration noise density                                      | FS bit set to 00                          |      | 218                 |      | µg/√Hz   |

| Vst    | Self-test output change <sup>(6),(7),(8)</sup>                  | FS bit set to 00<br>X axis                | 120  | 300                 | 550  | Lsb      |

|        |                                                                 | FS bit set to 00<br>Y axis                | 120  | 300                 | 550  | Lsb      |

|        |                                                                 | FS bit set to 00<br>Z axis                | 140  | 350                 | 750  | Lsb      |

| Top    | Operating temperature range                                     |                                           | -40  |                     | +85  | °C       |

| Wh     | Product weight                                                  |                                           |      | 20                  |      | mgram    |

1. The product is factory calibrated at 2.5 V. The operational power supply range is from 2.16 V to 3.6 V.

2. Typical specifications are not guaranteed

3. Verified by wafer level test and measurement of initial offset and sensitivity

4. Typical zero-*g* level offset value after MSL3 preconditioning

5. Offset can be eliminated by enabling the built-in high pass filter

6. The sign of "Self-test output change" is defined by CTRL\_REG4 STsign bit (Table 28), for all axes

7. Self-test output changes with the power supply. "Self-test output change" is defined as  $\text{OUTPUT[Lsb]}_{(\text{CTRL\_REG4 ST bit}=1)} - \text{OUTPUT[Lsb]}_{(\text{CTRL\_REG4 ST bit}=0)}$ . 1Lsb=4g/4096 at 12bit representation, ±2 g Full-scale

8. Output data reach 99% of final value after 1/ODR+ 1 ms when enabling self-test mode, due to device filtering

**Registre de stockage** des accélérations mesurées sur les axes X, Y et Z (en complément à 2, représentation sur 16 bits) :

**Table 15. Register address map**

| Name                     | Type | Register address |          | Default  | Comment        |

|--------------------------|------|------------------|----------|----------|----------------|

|                          |      | Hex              | Binary   |          |                |

| Reserved (do not modify) |      | 00 - 0E          |          |          | Reserved       |

| WHO_AM_I                 | r    | 0F               | 000 1111 | 00110010 | Dummy register |

| Reserved (do not modify) |      | 10 - 1F          |          |          | Reserved       |

| CTRL_REG1                | rw   | 20               | 010 0000 | 00000111 |                |

| CTRL_REG2                | rw   | 21               | 010 0001 | 00000000 |                |

| CTRL_REG3                | rw   | 22               | 010 0010 | 00000000 |                |

| CTRL_REG4                | rw   | 23               | 010 0011 | 00000000 |                |

| CTRL_REG5                | rw   | 24               | 010 0100 | 00000000 |                |

| HP_FILTER_RESET          | r    | 25               | 010 0101 |          | Dummy register |

| REFERENCE                | rw   | 26               | 010 0110 | 00000000 |                |

| STATUS_REG               | r    | 27               | 010 0111 | 00000000 |                |

| OUT_X_L                  | r    | 28               | 010 1000 | output   |                |

| OUT_X_H                  | r    | 29               | 010 1001 | output   |                |

| OUT_Y_L                  | r    | 2A               | 010 1010 | output   |                |

| OUT_Y_H                  | r    | 2B               | 010 1011 | output   |                |

| OUT_Z_L                  | r    | 2C               | 010 1100 | output   |                |

| OUT_Z_H                  | r    | 2D               | 010 1101 | output   |                |

| Reserved (do not modify) |      | 2E - 2F          |          |          | Reserved       |

| INT1_CFG                 | rw   | 30               | 011 0000 | 00000000 |                |

| INT1_SOURCE              | r    | 31               | 011 0001 | 00000000 |                |

| INT1_THS                 | rw   | 32               | 011 0010 | 00000000 |                |

| INT1_DURATION            | rw   | 33               | 011 0011 | 00000000 |                |

| INT2_CFG                 | rw   | 34               | 011 0100 | 00000000 |                |

| INT2_SOURCE              | r    | 35               | 011 0101 | 00000000 |                |

| INT2_THS                 | rw   | 36               | 011 0110 | 00000000 |                |

| INT2_DURATION            | rw   | 37               | 011 0111 | 00000000 |                |

| Reserved (do not modify) |      | 38 - 3F          |          |          | Reserved       |

Registers marked as *Reserved* must not be changed. The writing to those registers may cause permanent damages to the device.

## Rôle fonctionnel des entrées et des sorties :

Block diagram and pin description

LIS331DLH

Table 2. Pin description

| Pin# | Name              | Function                                                                                                       |

|------|-------------------|----------------------------------------------------------------------------------------------------------------|

| 1    | Vdd_IO            | Power supply for I/O pins                                                                                      |

| 2    | NC                | Not connected                                                                                                  |

| 3    | NC                | Not connected                                                                                                  |

| 4    | SCL<br>SPC        | I <sup>2</sup> C serial clock (SCL)<br>SPI serial port clock (SPC)                                             |

| 5    | GND               | 0V supply                                                                                                      |

| 6    | SDA<br>SDI<br>SDO | I <sup>2</sup> C serial data (SDA)<br>SPI serial data input (SDI)<br>3-wire interface serial data output (SDO) |

| 7    | SDO<br>SA0        | SPI serial data output (SDO)<br>I <sup>2</sup> C less significant bit of the device address (SA0)              |

| 8    | CS                | SPI enable<br>I <sup>2</sup> C/SPI mode selection (1: I <sup>2</sup> C mode; 0: SPI enabled)                   |

| 9    | INT 2             | Inertial interrupt 2                                                                                           |

| 10   | Reserved          | Connect to GND                                                                                                 |

| 11   | INT 1             | Inertial interrupt 1                                                                                           |

| 12   | GND               | 0 V supply                                                                                                     |

| 13   | GND               | 0 V supply                                                                                                     |

| 14   | Vdd               | Power supply                                                                                                   |

| 15   | Reserved          | Connect to Vdd                                                                                                 |

| 16   | GND               | 0 V supply                                                                                                     |

## Procédure de lecture de l'accélération Ax sur la liaison SPI :

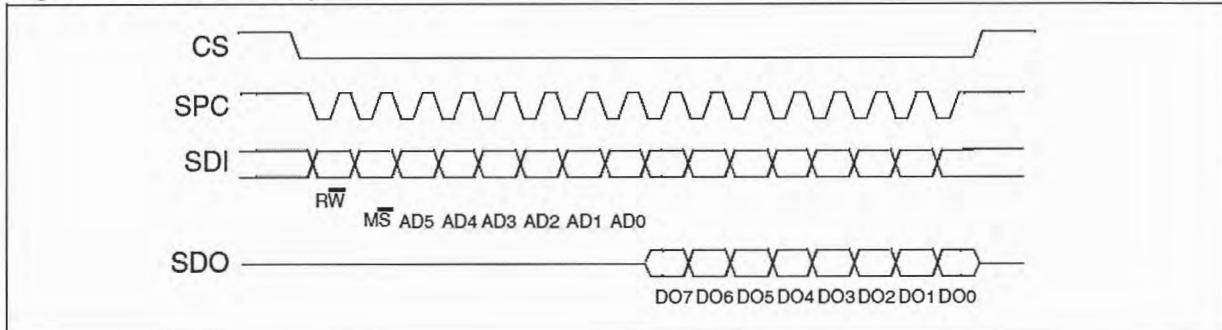

La communication entre l'accéléromètre et le microcontrôleur, sur le bus SPI, lors de la lecture de plusieurs octets est décrite sur le chronogramme ci-dessous.

Figure 7. SPI read protocol

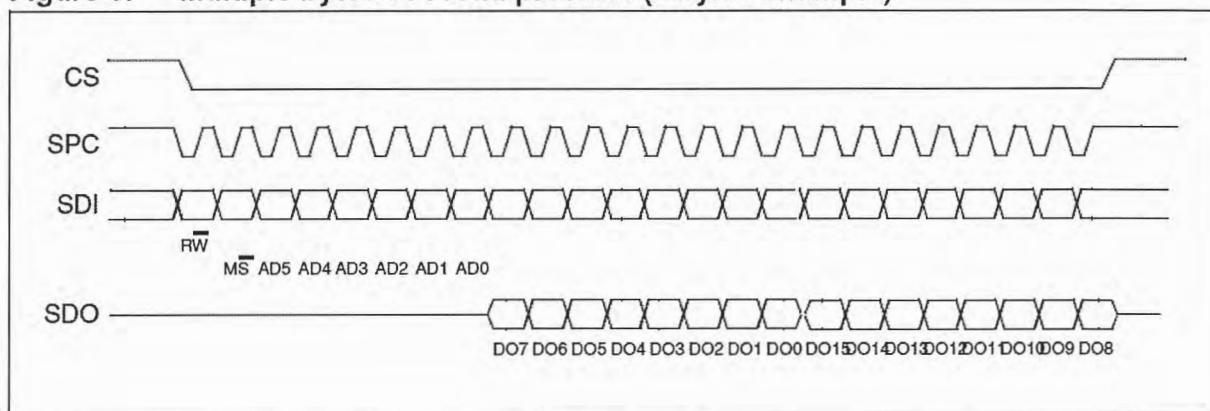

Cas particulier « multibyte read sequence » :

The SPI Read command is performed with 16 clock pulses. Multiple byte read command is performed adding blocks of 8 clock pulses at the previous one.

**bit 0:** READ bit. The value is 1.

**bit 1:**  $\overline{MS}$  bit. When 0 do not increment address, when 1 increment address in multiple reading.

**bit 2-7:** address AD(5:0). This is the address field of the indexed register.

**bit 8-15:** data DO(7:0) (read mode). This is the data that will be read from the device (MSb first).

**bit 16-...** : data DO(...-8). Further data in multiple byte reading.

**Figure 8. Multiple bytes SPI read protocol (2 bytes example)**

## Annexe A2

Extraits de la documentation technique de l'amplificateur opérationnel LF357.

**LF155, LF156, LF355, LF356, LF357**

SNOSBH0C – MAY 2000 – REVISED MARCH 2013

[www.ti.com](http://www.ti.com)

### DC Electrical Characteristics

| Symbol                     | Parameter                                 | Conditions                     | LF155/6  |           |     | LF256/7<br>LF356B |           |     | LF355/6/7 |           |     | Units                   |

|----------------------------|-------------------------------------------|--------------------------------|----------|-----------|-----|-------------------|-----------|-----|-----------|-----------|-----|-------------------------|

|                            |                                           |                                | Min      | Typ       | Max | Min               | Typ       | Max | Min       | Typ       | Max |                         |

| $V_{OS}$                   | Input Offset Voltage                      | $R_S=50\Omega, T_A=25^\circ C$ |          | 3         | 5   |                   | 3         | 5   |           | 3         | 10  | mV                      |

|                            |                                           | Over Temperature               |          |           | 7   |                   |           | 6.5 |           |           | 13  | mV                      |

| $\Delta V_{OS}/\Delta T$   | Average TC of Input Offset Voltage        | $R_S=50\Omega$                 |          | 5         |     |                   | 5         |     |           | 5         |     | $\mu V/^\circ C$        |

| $\Delta T_C/\Delta V_{OS}$ | Change in Average TC with $V_{OS}$ Adjust | $R_S=50\Omega, (2)$            |          | 0.5       |     |                   | 0.5       |     |           | 0.5       |     | $\mu V/^\circ C$ per mV |

| $I_{OS}$                   | Input Offset Current                      | $T_J=25^\circ C, (1) (3)$      |          | 3         | 20  |                   | 3         | 20  |           | 3         | 50  | pA                      |

|                            |                                           | $T_J \leq T_{HIGH}$            |          |           | 20  |                   |           | 1   |           |           | 2   | nA                      |

| $I_B$                      | Input Bias Current                        | $T_J=25^\circ C, (1) (3)$      |          | 30        | 100 |                   | 30        | 100 |           | 30        | 200 | pA                      |

|                            |                                           | $T_J \leq T_{HIGH}$            |          |           | 50  |                   |           | 5   |           |           | 8   | nA                      |

| $R_{IN}$                   | Input Resistance                          | $T_J=25^\circ C$               |          | $10^{12}$ |     |                   | $10^{12}$ |     |           | $10^{12}$ |     | $\Omega$                |

| $A_{VOL}$                  | Large Signal Voltage Gain                 | $V_S=\pm 15V, T_A=25^\circ C$  | 50       | 200       |     | 50                | 200       |     | 25        | 200       |     | V/mV                    |

|                            |                                           | $V_O=\pm 10V, R_L=2k$          |          |           |     |                   |           |     |           |           |     |                         |

|                            |                                           | Over Temperature               | 25       |           |     | 25                |           |     | 15        |           |     | V/mV                    |

| $V_O$                      | Output Voltage Swing                      | $V_S=\pm 15V, R_L=10k$         | $\pm 12$ | $\pm 13$  |     | $\pm 12$          | $\pm 13$  |     | $\pm 12$  | $\pm 13$  |     | V                       |

|                            |                                           | $V_S=\pm 15V, R_L=2k$          | $\pm 10$ | $\pm 12$  |     | $\pm 10$          | $\pm 12$  |     | $\pm 10$  | $\pm 12$  |     | V                       |

| $V_{CM}$                   | Input Common-Mode Voltage Range           | $V_S=\pm 15V$                  | $\pm 11$ | +15.1     |     | $\pm 11$          | +15.1     |     | $+10$     | +15.1     |     | V                       |

|                            |                                           |                                |          | -12       |     |                   | -12       |     |           | -12       |     | V                       |

| CMRR                       | Common-Mode Rejection Ratio               |                                |          | 85        | 100 |                   | 85        | 100 |           | 80        | 100 | dB                      |

| PSRR                       | Supply Voltage Rejection Ratio            | (4)                            |          | 85        | 100 |                   | 85        | 100 |           | 80        | 100 | dB                      |

(1) Unless otherwise stated, these test conditions apply:

|                       | LF155/156                                | LF256/257                               | LF356B                                | LF355/6/7                             |

|-----------------------|------------------------------------------|-----------------------------------------|---------------------------------------|---------------------------------------|

| Supply Voltage, $V_S$ | $\pm 15V \leq V_S \leq \pm 20V$          | $\pm 15V \leq V_S \leq \pm 20V$         | $\pm 15V \leq V_S \leq \pm 20V$       | $V_S = \pm 15V$                       |

| $T_A$                 | $-55^\circ C \leq T_A \leq +125^\circ C$ | $-25^\circ C \leq T_A \leq +85^\circ C$ | $0^\circ C \leq T_A \leq +70^\circ C$ | $0^\circ C \leq T_A \leq +70^\circ C$ |

| $T_{HIGH}$            | $+125^\circ C$                           | $+85^\circ C$                           | $+70^\circ C$                         | $+70^\circ C$                         |

and  $V_{OS}$ ,  $I_B$  and  $I_{OS}$  are measured at  $V_{CM} = 0$ .

- (2) The Temperature Coefficient of the adjusted input offset voltage changes only a small amount ( $0.5\mu V/^\circ C$  typically) for each mV of adjustment from its original unadjusted value. Common-mode rejection and open loop voltage gain are also unaffected by offset adjustment.

- (3) The input bias currents are junction leakage currents which approximately double for every  $10^\circ C$  increase in the junction temperature,  $T_J$ . Due to limited production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation,  $P_d$ .  $T_J = T_A + \theta_{JA} P_d$  where  $\theta_{JA}$  is the thermal resistance from junction to ambient. Use of a heat sink is recommended if input bias current is to be kept to a minimum.

- (4) Supply Voltage Rejection is measured for both supply magnitudes increasing or decreasing simultaneously, in accordance with common practice.

### DC Electrical Characteristics

$T_A = T_J = 25^\circ C, V_S = \pm 15V$

| Parameter      | LF155 |     | LF355 |     | LF156/256/257/356B |     | LF356 |     | LF357 |     | Units |

|----------------|-------|-----|-------|-----|--------------------|-----|-------|-----|-------|-----|-------|

|                | Typ   | Max | Typ   | Max | Typ                | Max | Typ   | Max | Typ   | Max |       |

| Supply Current | 2     | 4   | 2     | 4   | 5                  | 7   | 5     | 10  | 5     | 10  | mA    |

## AC Electrical Characteristics

$T_A = T_J = 25^\circ\text{C}$ ,  $V_S = \pm 15\text{V}$

| Symbol   | Parameter                      | Conditions         | LF155/355 | LF156/256/<br>356B | LF156/256/356/<br>LF356B | LF257/357 | Units                        |

|----------|--------------------------------|--------------------|-----------|--------------------|--------------------------|-----------|------------------------------|

|          |                                |                    | Typ       | Min                | Typ                      | Typ       |                              |

| SR       | Slew Rate                      | LF155/6: $A_V=1$ , | 5         | 7.5                | 12                       |           | $\text{V}/\mu\text{s}$       |

|          |                                | LF357: $A_V=5$     |           |                    |                          | 50        | $\text{V}/\mu\text{s}$       |

| GBW      | Gain Bandwidth Product         |                    | 2.5       |                    | 5                        | 20        | MHz                          |

| $t_s$    | Settling Time to 0.01%         | (1)                | 4         |                    | 1.5                      | 1.5       | $\mu\text{s}$                |

| $e_n$    | Equivalent Input Noise Voltage | $R_S=100\Omega$    |           |                    |                          |           |                              |

|          |                                | $f=100\text{ Hz}$  | 25        |                    | 15                       | 15        | $\text{nV}/\sqrt{\text{Hz}}$ |

|          |                                | $f=1000\text{ Hz}$ | 20        |                    | 12                       | 12        | $\text{nV}/\sqrt{\text{Hz}}$ |

| $i_n$    | Equivalent Input Current Noise | $f=100\text{ Hz}$  | 0.01      |                    | 0.01                     | 0.01      | $\text{pA}/\sqrt{\text{Hz}}$ |

|          |                                | $f=1000\text{ Hz}$ | 0.01      |                    | 0.01                     | 0.01      | $\text{pA}/\sqrt{\text{Hz}}$ |

| $C_{IN}$ | Input Capacitance              |                    | 3         |                    | 3                        | 3         | pF                           |

- (1) Settling time is defined here, for a unity gain inverter connection using 2 k $\Omega$  resistors for the LF155/6. It is the time required for the error voltage (the voltage at the inverting input pin on the amplifier) to settle to within 0.01% of its final value from the time a 10V step input is applied to the inverter. For the LF357,  $A_V = -5$ , the feedback resistor from output to input is 2k $\Omega$  and the output step is 10V (See Settling Time Test Circuit).

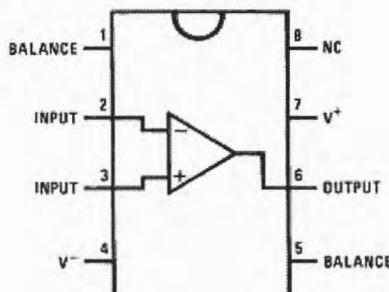

**Figure 35. SOIC and PDIP Package (D and P)

See Package Number

D (R-PDSO-G8) or P (R-PDIP-T8)**

## Annexe A3

Extraits de la documentation technique du convertisseur AD7530 :

# **AD7520, AD7530, AD7521, AD7531**

August 1997

## 10-Bit, 12-Bit, Multiplying D/A Converters

### **Features**

- AD7520/AD7530, 10-Bit Resolution; 8-Bit, 9-Bit and 10-Bit Linearity

- AD7521/AD7531, 12-Bit Resolution; 8-Bit, 9-Bit and 10-Bit Linearity

- Low Power Dissipation (Max) ..... 20mW

- Low Nonlinearity Tempco at 2ppm of FSR/°C

- Current Settling Time to 0.05% of FSR ..... 1.0µs

- Supply Voltage Range ..... ±5V to +15V

- TTL/CMOS Compatible

- Full Input Static Protection

- /883B Processed Versions Available

### **Description**

The AD7520/AD7530 and AD7521/AD7531 are monolithic, high accuracy, low cost 10-bit and 12-bit resolution, multiplying digital-to-analog converters (DAC). Intersil's thin-film on CMOS processing gives up to 10-bit accuracy with TTL/CMOS compatible operation. Digital inputs are fully protected against static discharge by diodes to ground and positive supply.

Typical applications include digital/analog interfacing, multiplication and division, programmable power supplies, CRT character generation, digitally controlled gain circuits, integrators and attenuators, etc.

The AD7530 and AD7531 are identical to the AD7520 and AD7521, respectively, with the exception of output leakage current and feedthrough specifications.

### **Ordering Information**

| PART NUMBER             | LINEARITY (INL, DNL) | TEMP. RANGE (°C) | PACKAGE      | PKG. NO. |

|-------------------------|----------------------|------------------|--------------|----------|

| AD7520JN, AD7530JN      | 0.2% (8-Bit)         | 0 to 70          | 16 Ld PDIP   | E16.3    |

| AD7520KN, AD7530KN      | 0.1% (9-Bit)         | 0 to 70          | 16 Ld PDIP   | E16.3    |

| AD7521JN, AD7531JN      | 0.2% (8-Bit)         | 0 to 70          | 18 Ld PDIP   | E18.3    |

| AD7521KN, AD7531KN      | 0.1% (9-Bit)         | 0 to 70          | 18 Ld PDIP   | E18.3    |

| AD7520LN, AD7530LN      | 0.05% (10-Bit)       | -40 to 85        | 16 Ld PDIP   | E16.3    |

| AD7521LN, AD7531LN      | 0.05% (10-Bit)       | -40 to 85        | 18 Ld PDIP   | E18.3    |

| AD7520JD                | 0.2% (8-Bit)         | -25 to 85        | 16 Ld CERDIP | F16.3    |

| AD7520KD                | 0.1% (9-Bit)         | -25 to 85        | 16 Ld CERDIP | F16.3    |

| AD7520LD                | 0.05% (10-Bit)       | -25 to 85        | 16 Ld CERDIP | F16.3    |

| AD7520SD, AD7520SD/883B | 0.2% (8-Bit)         | -55 to 125       | 16 Ld CERDIP | F16.3    |

| AD7520UD, AD7520UD/883B | 0.05% (10-Bit)       | -55 to 125       | 16 Ld CERDIP | F16.3    |

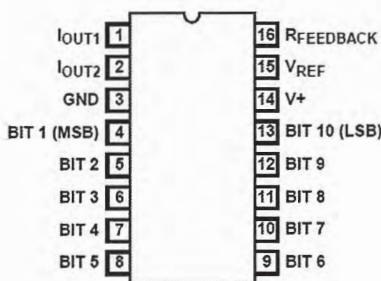

### **Pinouts**

AD7520, AD7530

(CERDIP, PDIP)

TOP VIEW

AD7521, AD7531

(PDIP)

TOP VIEW

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

<http://www.intersil.com> or 407-727-9207 | Copyright © Intersil Corporation 1999

File Number **3104.1**

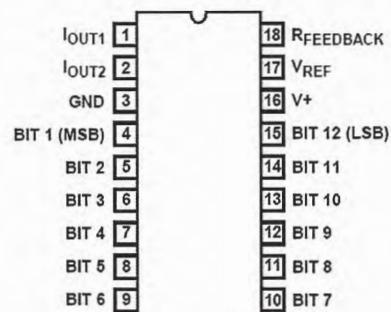

## Functional Diagram

### NOTES:

Switches shown for Digital Inputs "High".

Resistor values are typical.

**Electrical Specifications**  $V_+ = +15V$ ,  $V_{REF} = +10V$ ,  $T_A = 25^{\circ}C$  Unless Otherwise Specified

| PARAMETER                                 | TEST CONDITIONS                                                                                | AD7520/AD7530 |           |                            | AD7521/AD7531 |           |                            | UNITS                      |

|-------------------------------------------|------------------------------------------------------------------------------------------------|---------------|-----------|----------------------------|---------------|-----------|----------------------------|----------------------------|

|                                           |                                                                                                | MIN           | TYP       | MAX                        | MIN           | TYP       | MAX                        |                            |

| <b>SYSTEM PERFORMANCE</b> (Note 2)        |                                                                                                |               |           |                            |               |           |                            |                            |

| Resolution                                |                                                                                                | 10            | 10        | 10                         | 12            | 12        | 12                         | Bits                       |

| Nonlinearity                              | J, S<br>S Over $-55^{\circ}C$ to $125^{\circ}C$<br>(Notes 2, 5) (Figure 3)                     | -             | -         | $\pm 0.2$<br>(8-Bit)       | -             | -         | $\pm 0.2$<br>(8-Bit)       | % of<br>FSR                |

|                                           | K<br>T Over $-55^{\circ}C$ to $125^{\circ}C$<br>(Figure 2)                                     | -             | -         | $\pm 0.1$<br>(9-Bit)       | -             | -         | $\pm 0.1$<br>(9-Bit)       | % of<br>FSR                |

|                                           | L, U<br>$-10V \leq V_{REF} \leq +10V$<br>U Over $-55^{\circ}C$ to $125^{\circ}C$<br>(Figure 2) | -             | -         | $\pm 0.05$<br>(10-Bit)     | -             | -         | $\pm 0.05$<br>(10-Bit)     | % of<br>FSR                |

| Nonlinearity Tempco                       | $-10V \leq V_{REF} \leq +10V$<br>(Notes 3, 4)                                                  | -             | -         | $\pm 2$                    | -             | -         | $\pm 2$                    | ppm of<br>FSR/ $^{\circ}C$ |

| Gain Error                                |                                                                                                | -             | $\pm 0.3$ | -                          | -             | $\pm 0.3$ | -                          | % of<br>FSR                |

| Gain Error Tempco                         |                                                                                                | -             | -         | $\pm 10$                   | -             | -         | $\pm 10$                   | ppm of<br>FSR/ $^{\circ}C$ |

| Output Leakage Current<br>(Either Output) | Over the Specified<br>Temperature Range                                                        | -             | -         | $\pm 200$<br>( $\pm 300$ ) | -             | -         | $\pm 200$<br>( $\pm 300$ ) | nA                         |

| <b>DYNAMIC CHARACTERISTICS</b>            |                                                                                                |               |           |                            |               |           |                            |                            |

| Output Current Settling Time              | To 0.05% of FSR (All Digital<br>Inputs Low To High And High<br>To Low) (Note 4) (Figure 7)     | -             | 1.0       | -                          | -             | 1.0       | -                          | $\mu s$                    |

| Feedthrough Error                         | $V_{REF} = 20V_{P-P}$ , 10kHz<br>(50kHz) All Digital Inputs Low<br>(Note 4) (Figure 6)         | -             | -         | 10                         | -             | -         | 10                         | mV <sub>P-P</sub>          |

| <b>REFERENCE INPUT</b>                    |                                                                                                |               |           |                            |               |           |                            |                            |

| Input Resistance                          | All Digital Inputs High<br>$I_{OUT1}$ at Ground                                                | 5             | 10        | 20                         | 5             | 10        | 20                         | k $\Omega$                 |

| <b>ANALOG OUTPUT</b>                      |                                                                                                |               |           |                            |               |           |                            |                            |

| Output Capacitance                        | $I_{OUT1}$<br>All Digital Inputs High<br>(Note 4) (Figure 5)                                   | -             | 200       | -                          | -             | 200       | -                          | pF                         |

|                                           | $I_{OUT2}$<br>All Digital Inputs Low<br>(Note 4) (Figure 5)                                    | -             | 75        | -                          | -             | 75        | -                          | pF                         |

|                                           | $I_{OUT1}$<br>All Digital Inputs Low<br>(Note 4) (Figure 5)                                    | -             | 75        | -                          | -             | 75        | -                          | pF                         |

|                                           | $I_{OUT2}$<br>All Digital Inputs Low<br>(Note 4) (Figure 5)                                    | -             | 200       | -                          | -             | 200       | -                          | pF                         |

**Electrical Specifications**  $V_+ = +15V$ ,  $V_{REF} = +10V$ ,  $T_A = 25^{\circ}C$  Unless Otherwise Specified (Continued)

| PARAMETER                           | TEST CONDITIONS                                                 | AD7520/AD7530        |                           |         | AD7521/AD7531 |                           |         | UNITS                    |

|-------------------------------------|-----------------------------------------------------------------|----------------------|---------------------------|---------|---------------|---------------------------|---------|--------------------------|

|                                     |                                                                 | MIN                  | TYP                       | MAX     | MIN           | TYP                       | MAX     |                          |

| Output Noise                        | Both Outputs<br>(Note 4) (Figure 4)                             | -                    | Equivalent to $10k\Omega$ | -       | -             | Equivalent to $10k\Omega$ | -       | Johnson Noise            |

| <b>DIGITAL INPUTS</b>               |                                                                 |                      |                           |         |               |                           |         |                          |

| Low State Threshold, $V_{IL}$       | Over the Specified Temperature Range<br>$V_{IN} = 0V$ or $+15V$ | -                    | -                         | 0.8     | -             | -                         | 0.8     | V                        |

| High State Threshold, $V_{IH}$      |                                                                 | 2.4                  | -                         | -       | 2.4           | -                         | -       | V                        |

| Input Current, $I_{IL}, I_{IH}$     |                                                                 | -                    | -                         | $\pm 1$ | -             | -                         | $\pm 1$ | $\mu A$                  |

| Input Coding                        | See Tables 1 and 2                                              | Binary/Offset Binary |                           |         |               |                           |         |                          |

| <b>POWER SUPPLY CHARACTERISTICS</b> |                                                                 |                      |                           |         |               |                           |         |                          |

| Power Supply Rejection              | $V_+ = 14.5V$ to $15.5V$<br>(Note 3) (Figure 3)                 | -                    | $\pm 0.005$               | -       | -             | $\pm 0.005$               | -       | % FSR/<br>% $\Delta V_+$ |

| Power Supply Voltage Range          |                                                                 | +5 to +15            |                           |         | +5 to +15     |                           |         | V                        |

| I <sub>+</sub>                      | All Digital Inputs at 0V or $V_+$<br>Excluding Ladder Network   | -                    | $\pm 1$                   | -       | -             | $\pm 1$                   | -       | $\mu A$                  |

|                                     | All Digital Inputs High or Low<br>Excluding Ladder Network      | -                    | -                         | 2       | -             | -                         | 2       | mA                       |

| Total Power Dissipation             | Including the Ladder Network                                    | -                    | 20                        | -       | -             | 20                        | -       | mW                       |

NOTES:

2. Full scale range (FSR) is 10V for Unipolar and  $\pm 10V$  for Bipolar modes.

3. Using internal feedback resistor  $R_{FEEDBACK}$ .

4. Guaranteed by design, or characterization and not production tested.

5. Accuracy not guaranteed unless outputs at GND potential.

6. Accuracy is tested and guaranteed at  $V_+ = 15V$  only.

**Nom :**

**Prénom :**

**N° d'inscription :**           /   /

(Le numéro est celui qui figure sur la convocation ou la feuille d'émargement)

**Concours**

**Section/Option**

**Epreuve**

**Matière**

EAE SIE 2

# DR1 - DR2 - DR3

Tournez la page S.V.P.

(E)

## Document réponse DR1

Associé à la partie I, Q3

*Code C++ ci-dessous à compléter (au niveau encadré):*

```

Bool C_CCD ::extract_CCD_img(void)

{

int x,y ;

for (x=0 ;x<640 ;x++)

{

for (y=0 ; y<480 ; y++)

{

img_in[...][...] =

}

}

;

return TRUE ;

}

```

## Document réponse DR2

Associé à la partie II, Q13 et Q14.

**Q13 :**

| Ligne | Position | Accélération sur X <sub>C</sub>                                                                          | Accélération sur Y <sub>C</sub>                                                               | Accélération sur Z <sub>C</sub>                                                               |

|-------|----------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 1     | (a)      | -1g <input type="checkbox"/><br>0g <input checked="" type="checkbox"/> x<br>+1g <input type="checkbox"/> | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/> x | -1g <input type="checkbox"/><br>0g <input type="checkbox"/> x<br>+1g <input type="checkbox"/> |

| 2     | (b)      | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>              | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>   | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>   |

| 3     | (c)      | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>              | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>   | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>   |

| 4     | (d)      | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>              | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>   | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>   |

| 5     | (e)      | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>              | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>   | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>   |

| 6     | (f)      | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>              | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>   | -1g <input type="checkbox"/><br>0g <input type="checkbox"/><br>+1g <input type="checkbox"/>   |

**Q14 :**

## Document réponse DR3

Associé à la partie II, Q18

| Valeurs d'accélération sur axe Xc | Valeur de FS1..0 | OUT_X_H (hexa) | OUT_X_L (hexa) |

|-----------------------------------|------------------|----------------|----------------|

| 0g                                | 00               |                |                |

| 350mg                             | 00               |                |                |

| 1g                                | 00               |                |                |

| -350mg                            | 00               |                |                |

| -1g                               | 11               |                |                |

Tableau 2. Valeurs stockées dans l'accéléromètre

**Nom :**

**Prénom :**

**N° d'inscription :**           /   /

(Le numéro est celui qui figure sur la convocation ou la feuille d'émargement)

**Concours**

**Section/Option**

**Epreuve**

**Matière**

EAE SIE 2

## DR4 - DR5

Tournez la page S.V.P.

F

**Document réponse DR4**

Associé à la partie II, Q19, Q20 et Q22.

**Q19 & Q20 :**

**Q22:**

## Document réponse DR5

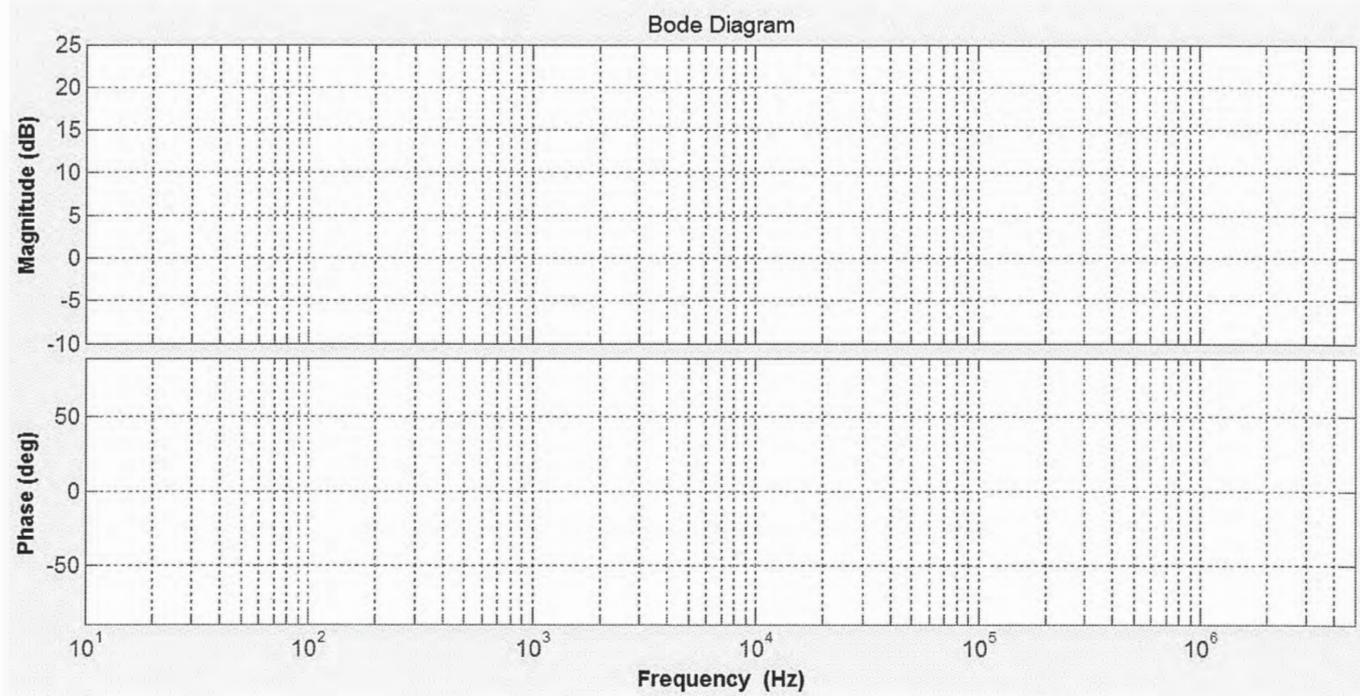

Associé à la partie III, Q41 & Q43.

Q41 : Diagramme de Bode asymptotique en module et en phase de la transmittance en boucle fermée  $T(p)$ .

Q43 : Diagramme de Bode asymptotique en module et en phase de la transmittance  $C(p)$ .